Hongzheng Chen Blog

FPGA结构、编译与应用

Feb 8th, 2019 0What is FPGA? Why FPGA?

可编程门阵列(Field-Programmable Gate Array, FPGA)是一种并行的非冯架构硬件,其最大的亮点就在于可编程/可重构(reconfigurable)。

由于FPGA的每个逻辑单元在重编程/烧写时已经确定,故它不需要指令,也不需共享内存。它的逻辑块、交互连接(interconnects)、IO接口都是可编程的。

FPGA的优势在于

- 比CPU快

- 比GPU省功耗

- 比ASIC便宜流片周期短

FPGA结构

FPGA上主要有两种资源,一种是逻辑(logic),一种是连接(interconnect)

逻辑资源

- 最底层的,用真值表可以实现绝大多数算法,真值表是FPGA计算的核心,即将几个简单的逻辑表达式整合为一个真值表

- 而实现真值表的硬件资源即为查找表(Look-up table, LUT),是FPGA最小计算单元;物理实施用N:1选择器(multiplexer)和N位存储器

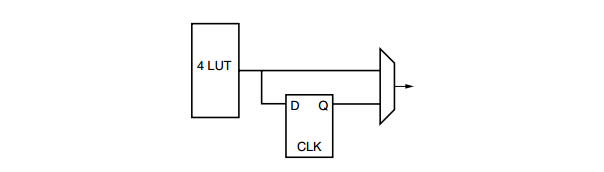

- LUT的大小和每个逻辑块内LUT的数量是需要关心的问题,目前大多FPGA采用4-LUT结构

-

LUT添加D触发器即可存储状态

- FPGA基本的存储单元为触发器(Flip-flop, FF),通常与LUT摆放在一起

-

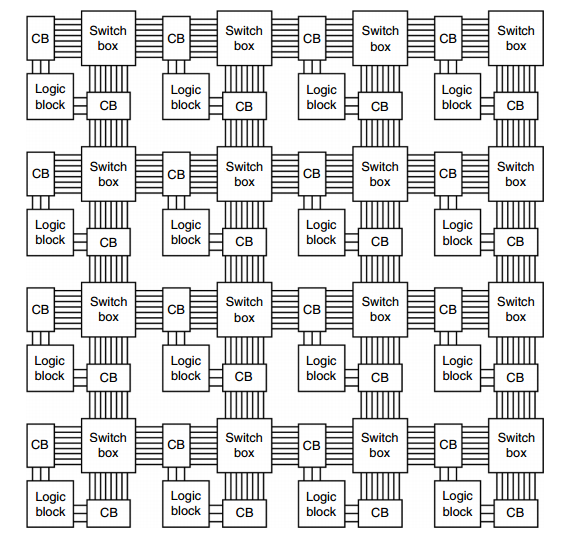

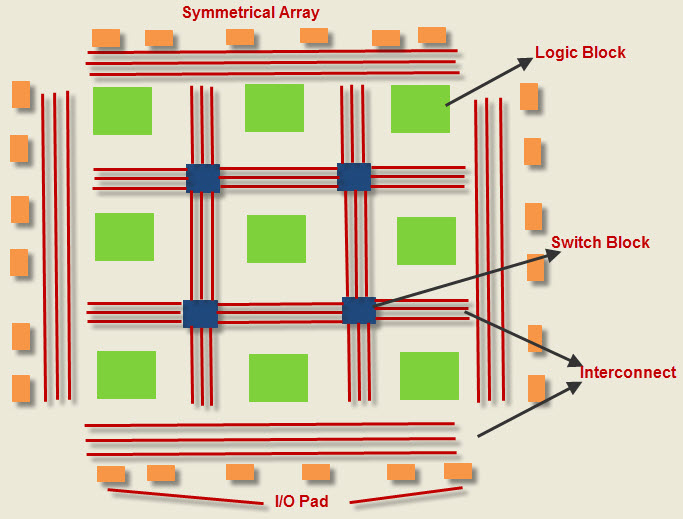

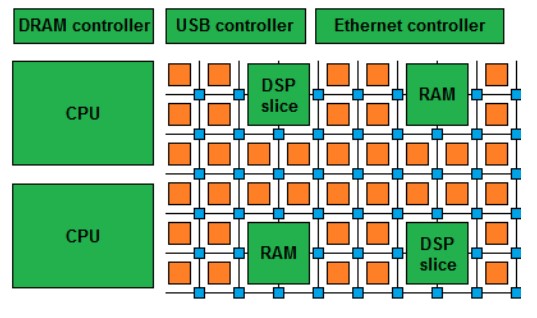

目前的FPGA采用岛式(island-style)结构,多个LUT构成一个逻辑块(logic/function block)。在Xilinx 7系列FPGA中,每个可配置逻辑块(configurable logic block, CLB)包含两个slice,每个slice包含4个LUT(以及多个FF和选择器)。

- 多个逻辑块就构成阵列(array)

这里每一个逻辑块就可以看成是岛屿,漂浮在交互连线的海洋上

连接资源

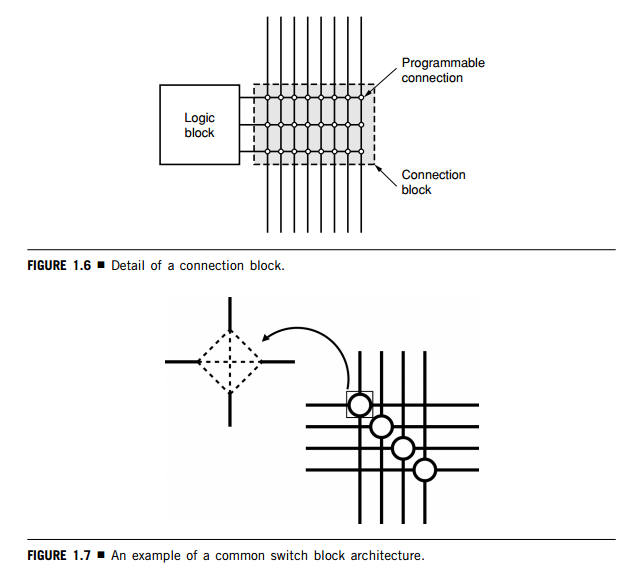

目前的FPGA结构则添加了连接块(connection block)和交换盒(switch box),将连接的部分从逻辑部分分离开来(连接块里是路由频道routing channel)

总结

- I/O:IO块

- CLB:Configurable Logic Block,逻辑块

- Memory:Block RAM (BRAM),片上内存

- BRAM是一个支持多种内存形式和接口的可配置随机储存器,可以储存字节,对字,全字,双字等等等,通常1个BRAM只有32K内存

- slice经过编写也可以储存数据(通过触发器),但这样做会增加额外消耗

- DSP:Digital Signal Processing

- 写死的(hardened)电路块,主要用来做乘加操作

现代的FPGA多采用异构架构,里面有定制化的DSP块,比LUT要快很多(可以理解成ASIC)

FPGA综合流程

要将软件程序映射到硬件上运行,就要通过编译(compilation),而在硬件中则通常称为综合(synthesis),下面是FPGA的主要综合流程(参照Xilinx Vivado的流程)

- 高层次综合(high-level synthesis, HLS):将高级程序语言C/C++编译为Verilog等硬件描述语言(HDL)

- 逻辑综合(logic synthesis):将HDL较为高层的逻辑结构转化为逻辑门/网表(netlist),指明连接关系

- 实施(implementation):Electronic Design Interchange Format(EDIF)

- 转译(translate):将所有网表及限制整合入一个大的平的(flat)网表,没有层次结构(hierarchy)

- 技术映射(technology mapping):将网表电路分组分配到每一个子块(sub-block)中 生成由查找表(Look-Up Table, LUT)构成的等价网表(RTL netlist),即将几个门整合为一个LUT

- 打包(clustering/packing):将几个子块整合到一起变成逻辑块聚(logic blocks clusters)

- 布局(placement):将这些子块放入FPGA的逻辑块(configurable logic block, CLB)中

- 布线(routing):在逻辑块之间连线,使得时序限制能够被满足

类比CPU一维的链接(link)寻址,FPGA的布局布线是二维的,主要优化area和delay

- 位流生成(bitstream)

- 验证(verification)/模拟(simulation)

- 行为(behavioural)仿真:在综合之前,检测逻辑错误

- 函数/网表(functional)仿真:在综合之后

- 时序(timing)仿真:在布局布线之后,最精确的仿真

FPGA的应用

- 搜索引擎(微软Bing、百度)

- 云计算(亚马逊)

- 深度学习(深鉴科技)

- 生物信息

- 图加速器

- …

FPGA的现状与未来

FPGA为什么尚未像GPU一样大范围推广?

FPGA发展到现在要解决的问题依然是效率(productivity)的问题,即如何让硬件工程师更快更好地编写调试硬件,甚至让软件工程师也能参与到硬件设计中,实现软硬件协同设计(hardware software co-design)。

关于FPGA的未来,在FCCM上有一个专门的预测栏目,最近的有在2016年预测2021年的。

学习资料

- Lastweek, Cook FPGA, https://github.com/lastweek/fpga_readings

- [日]天野英晴,《FPGA原理和结构》,人民邮电出版社,2019年4月1日

- Scott Hauck and Andre DeHon, Reconfigurable Computing: The Theory and Practice of FPGA-Based Computation, Elsevier Inc., 2008

参考资料

- 如何评价微软在数据中心使用 FPGA 代替传统 CPU 的做法? - 李博杰的回答 - 知乎 https://www.zhihu.com/question/24174597/answer/138717507

- https://www.design-reuse.com/articles/7330/fpga-programming-step-by-step.html

- https://indico.desy.de/indico/event/7001/session/0/contribution/1/material/slides/0.pdf

- Scott Hauck and André Dehon, Reconfigurable Computing - The Theory and Practice of FPGA-Based Computation, Elsevier, 2008, Online

- https://www.edgefx.in/fpga-architecture-applications/

- Farooq, U. et al., Tree-based Heterogeneous FPGA Architectures Application Specific Exploration and Optimization, Springer, 2012, Online

- LegUp Computing Inc., LegUp User Manual (v5.1) - User Guide, 2017