Hongzheng Chen Blog

Skylake架构简析

Feb 25th, 2019 0因为实验室服务器的CPU是Intel Xeon Gold系列,所以这里简要介绍一下Intel的Skylake-SP架构。

简介

- Skylake是2015年Intel提出的14nm新架构

- Skylake Scalable Processor (SP)针对服务器端

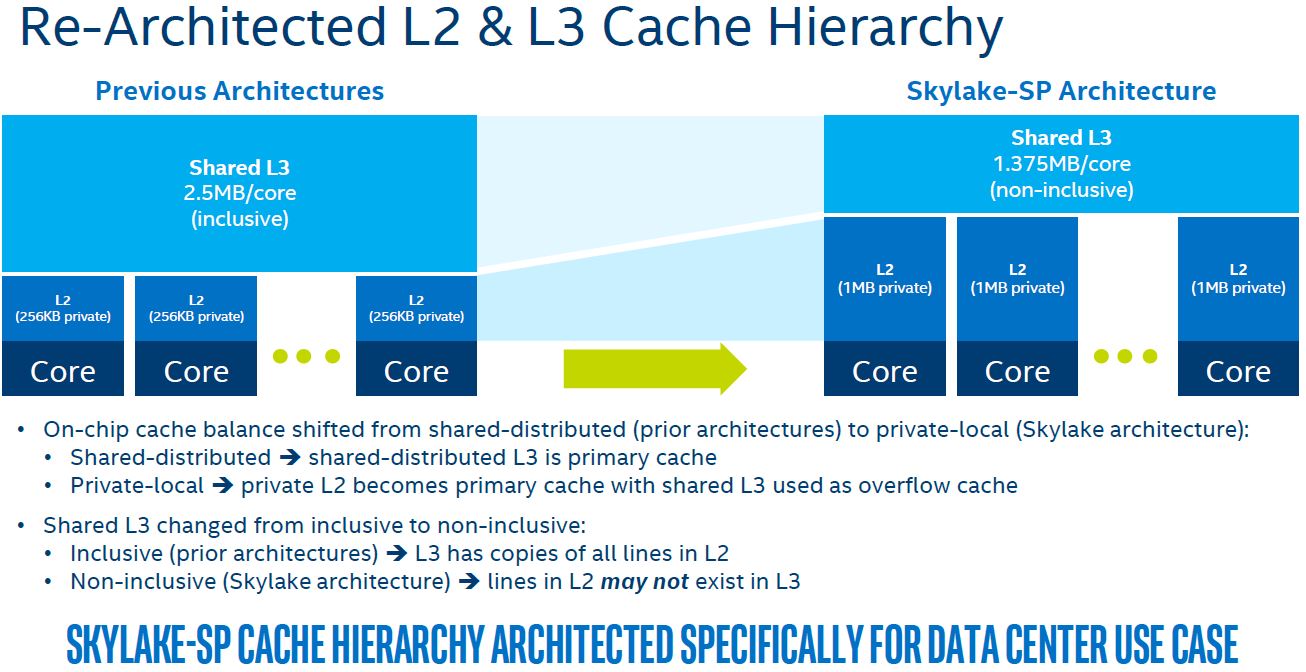

Skylake桌面版和Skylake服务器版(SP)最大的区别在于cache的层次结构不同了

实验室服务器Intel Gold 5118的cache层次结构如下

Cache Organization

L1$ 768 KiB

L1I$ 384 KiB 12x32 KiB 8-way set associative

L1D$ 384 KiB 12x32 KiB 8-way set associative write-back

L2$ 12 MiB

12x1 MiB 16-way set associative write-back

L3$ 16.5 MiB

12x1.375 MiB 11-way set associative write-back

更多的核,则需要更低的延迟,因而需要将更多数据放得更靠近CPU。(L2 cache比L3要快3.5-4倍)

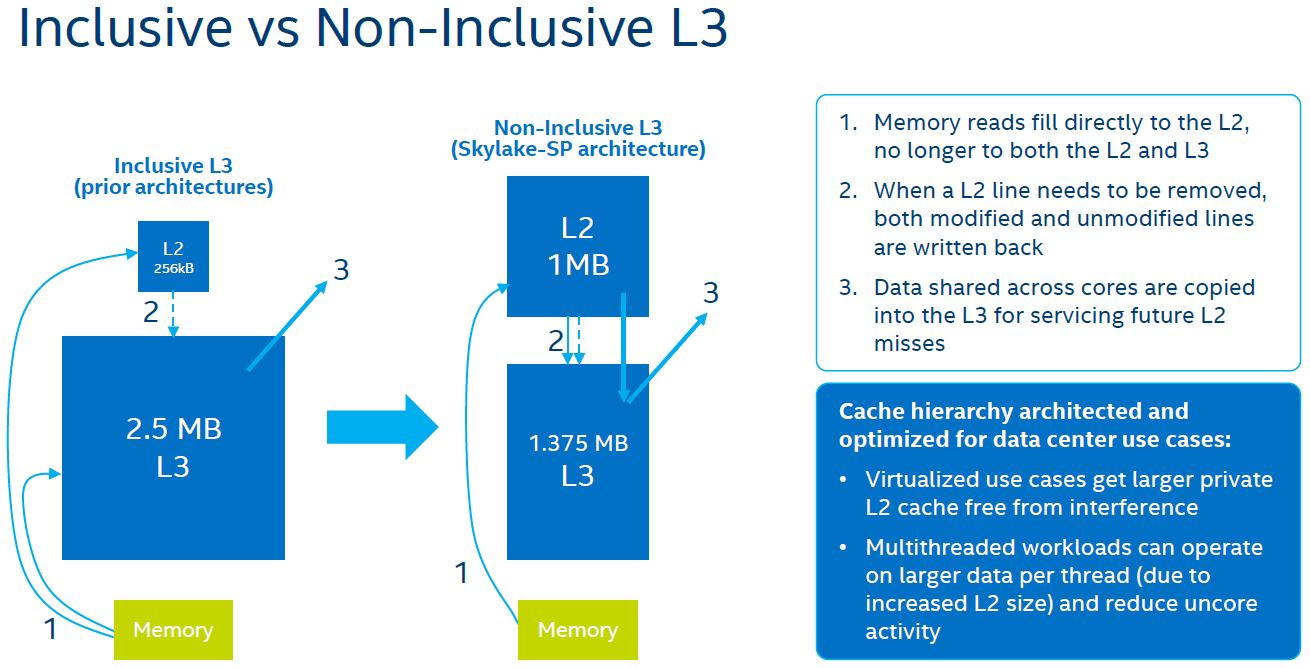

这里还有很重要一点在于,SP的L3 cache是不包含的(non-inclusive)

几点变化总结如下

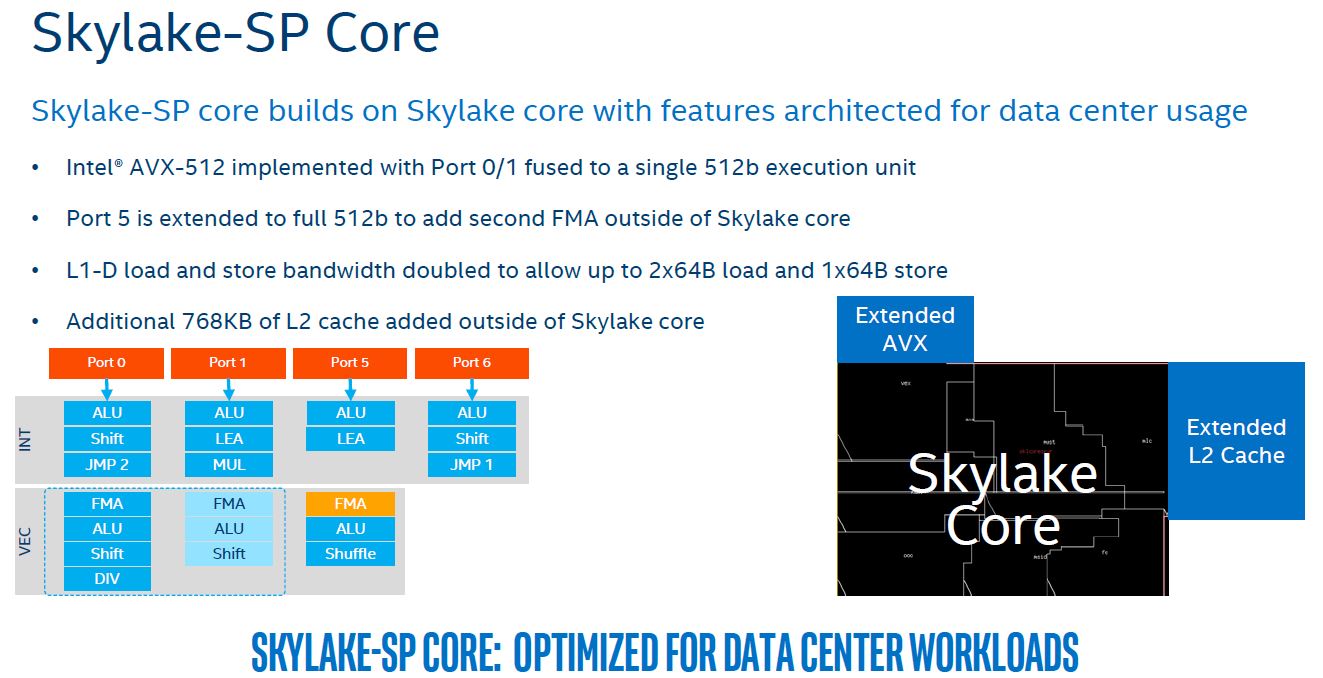

- cache层次结构改变

- AVX-512支持

- 扩展的融合乘积FMA单元

参考资料

- Intel Next Generation Microarchitecture Code Name Skylake, Intel Developer Forum, 2015, Online

- https://en.wikichip.org/wiki/intel/cores/skylake_sp

- Intel Xeon Scalable Processor Family Microarchitecture Overview, https://www.servethehome.com/intel-xeon-scalable-processor-family-microarchitecture-overview/

- Tick-tock model, https://en.wikipedia.org/wiki/Tick%E2%80%93tock_model